# Name\_\_\_\_\_

## EE 330

Exam 2 Fall 2020 (Oct 9 2020)

Instructions: There are 10 questions and 5 problems. The points allocated to each question and each problem are as indicated. Please solve problems in the space provided on this exam, on separate sheets of white paper, or on a tablet pc. When finished, scan or image and upload as a .pdf file on Canvas. Exams are due by 1:00 p.m.

Due to the online nature of this exam, students will be expected to adhere to the honor system and acknowledge adherence with a signature given below. This is an open-book open-notes exam and students can seek basic information using online resources but with the following absolute restrictions. Prior to the Canvas upload due time, no questions or problems should be posted on any electronic forum, no discussions are permitted relating to this exam with anyone else besides the course instructor, and no solutions obtained from any source other than by the student taking the exam is permitted. The course instructor will attempt to respond to questions by email that are sent between 11:00 a.m. and 1:00 p.m.

If parameters of semiconductor processes are needed beyond what is given in a specific problem or question, assume a CMOS process is available with the following key process parameters;  $\mu_n C_{OX}=100\mu A/V^2$ ,  $\mu_p C_{OX}=\mu_n C_{OX}/3$ ,  $V_{TNO}=0.5V$ ,  $V_{TPO}= -0.5V$ ,  $C_{OX}=8fF/\mu^2$ ,  $\lambda = 0$ . Correspondingly, assume all npn BJT transistors have model parameters  $J_S=10^{-14}A/\mu^2$  and  $\beta=100$  and all pnp BJT transistors have model parameters  $J_S=10^{-14}A/\mu^2$  and  $\beta=25$ . If the emitter area of a transistor is not given, assume it is  $100\mu^2$ . If reference to a diode is made, assume the process parameter  $J_S=10^{-17}A/\mu^2$ ,  $V_{GO}=1.17V$ , and m=2.3. The ratio of Boltzmann's constant to the charge of an electron is k/q=8.61E-5 V/K. If any other process parameters for MOS devices are needed, use the process parameters associated with the process described on the attachment to this exam. Specify clearly what process parameters you are using in any solution requiring process parameters.

Honor System Adherence Signature:

I certify that I have adhered to the honor system policy described in the second paragraph above \_\_\_\_\_

#### **Short Questions**

1. (2 pts) How many model parameters are there in a 16-bin binning model if each bin used a BSIM device model?

2. (2 pts) One of the models that was introduced for the MOS transistor was the  $\alpha$ -law model. Though it is more accurate than the square-law model for very small transistors, it is not used much. Why is the  $\alpha$ -law model not used much?

3. (2pts) Why is the  $\beta$  of the vertical transistor typically much larger than the  $\beta$  of a lateral transistor in a typical bipolar process?

4. (2 pts) Why is CVD used instead of thermal growth when placing a  $SiO_2$  layer on top of an aluminum interconnect?

5 (2 pts) True or False: When operating in the forward active region the BE junction of a BJT is forward biased and the BC junction is forward biased for npn transistors?

6. (2pts) What parameter in the model of the BJT models the slope of the output characteristics in the Forward Active region?

7. (2pts) Why is an epitaxial process used to create the collector region of a BJT instead of an n-type diffusion in a typical bipolar process?

8. (2pts) The term "increasing the power of a signal" is commonly used when describing an electronic amplifier. The input and output signals in an amplifier are, however, often voltages. What does it mean to "increase the power of a signal?" when the signals of interest are voltages?

9. (2pts) Through the 50's and 60's, bipolar processes were exclusively used to build integrated circuits with active devices. Why were the CMOS processes that are widely used today not used in the 50's and 60's?

10. (2pts) Why are designers not able to make a direct contact between Metal 2 and active in the standard CMOS process flow that was discussed in class?

#### Problems

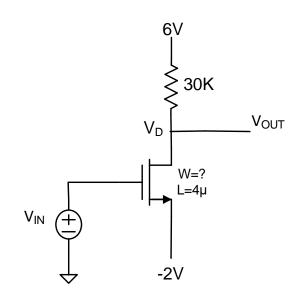

**Problem 1** (16 pt) Consider the following circuit.

- a) Determine W so that the quiescent output voltage is 0V

- b) If V<sub>IN</sub>=0.02sin(100t), determine the output voltage with the value of W determined in part a)

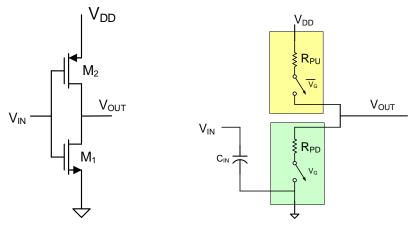

**Problem 2** A switch-level model for a digital inverter is shown below. If the supply voltage is 2.2V, determine the parameters in the switch-level model if the inverter is designed in the 0.18um process (model information attached to this exam) with dimensions  $L_1=L_2=0.5\mu m$  and  $W_1=W_2=4\mu m$ .

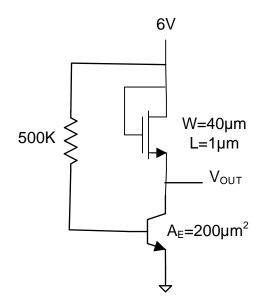

**Problem 3** Determine V<sub>OUT</sub>. Assume the bipolar transistor has parameters  $\beta$ =100 and J<sub>S</sub>=10<sup>-14</sup>A/ $\mu^2$  and the MOS transistor has parameters uCox=100 $\mu$ A/V<sup>2</sup> and V<sub>TH</sub>=1V.

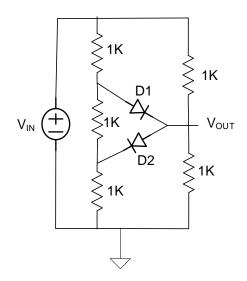

Problem 4 (16 pts)Consider the following circuit where the diodes areassumed to be modeled by the equation $\begin{cases} I_D = 0 & \text{if } V_D < 0.6V \\ V_D = 0.6V & \text{if } I_D > 0 \end{cases}$

- a) Determine V<sub>OUT</sub> if  $V_{IN} = 3V$

- b) For 0 < t < 6, obtain an expression for and plot  $V_{OUT}$  if  $V_{IN}=6t$

- c) Extra Credit (8 pts) Obtain an expression for and plot  $V_{OUT}(t)$  if  $V_{IN}(t)=6sin(10t)$  for one period of the input.

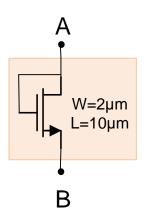

**Problem 5** (16 pts) Consider the following one-port where the MOS transistor has parameters  $V_{TN}=0.5V \ \mu_n C_{OX}=300 \mu AV^{-2}$  and  $\lambda=0$ . Assume the quiescent current was measured to be I<sub>Q</sub>=4mA.

- a) Determine the quiescent voltage between nodes A and B

- b) The small-signal equivalent circuit of any one-port at any Q-point is a resistor. Derive the small-signal equivalent of the one-port between nodes A and B at the Q-point specified.

| RUN:        | T68B (MM NON-EPI) |               | VENDOR:            |

|-------------|-------------------|---------------|--------------------|

| TSMC        | —                 |               |                    |

| TECHNOLOGY: | SCN018            |               | FEATURE SIZE: 0.18 |

| microns     |                   |               |                    |

|             |                   | Run type: SKD |                    |

INTRODUCTION: This report contains the lot average results obtained by MOSIS from measurements of MOSIS test structures on each wafer of this fabrication lot. SPICE parameters obtained from similar measurements on a selected wafer are also attached.

COMMENTS: DSCN6M018 TSMC

| TRANSISTOR PARAMETE                 | RS W/L    | N-CHANNEL            | P-CHANNEL             | UNITS                   |

|-------------------------------------|-----------|----------------------|-----------------------|-------------------------|

| MINIMUM<br>Vth                      | 0.27/0.18 | 0.50                 | -0.51                 | volts                   |

| SHORT<br>Idss<br>Vth<br>Vpt         | 20.0/0.18 | 547<br>0.51<br>4.8   | -250<br>-0.51<br>-5.6 | uA/um<br>volts<br>volts |

| WIDE<br>Ids0                        | 20.0/0.18 | 14.4                 | -4.7                  | pA/um                   |

| LARGE<br>Vth<br>Vjbkd<br>Ijlk       | 50/50     | 0.43<br>3.1<br><50.0 | -4.3                  | volts<br>volts<br>pA    |

| K' (Uo*Cox/2)<br>Low-field Mobility |           | 175.4<br>416.5       |                       |                         |

COMMENTS: Poly bias varies with design technology. To account for mask bias use the appropriate value for the parameters XL and XW in your SPICE model card.

|                        | Design Tech  | nnology          | Х                 | L (um)         | XW um) |  |  |

|------------------------|--------------|------------------|-------------------|----------------|--------|--|--|

|                        |              |                  |                   |                |        |  |  |

|                        | SCN6M_DEEP   | (lambda=0.09     | ) 0               | .00            | -0.01  |  |  |

|                        |              | thick oxid       | e 0               | .00            | -0.01  |  |  |

|                        | SCN6M_SUBM   | (lambda=0.10     | ) -0              | .02            | 0.00   |  |  |

|                        |              | thick oxid       | e -0              | .02            | 0.00   |  |  |

|                        |              |                  |                   |                |        |  |  |

| FOX TRANSISTORS<br>Vth | GATE<br>Poly | N+ACTIVE<br>>6.6 | P+ACTIVE<br><-6.6 | UNITS<br>volts |        |  |  |

PROCESS PARAMETERSN+P+POLYN+BLKPLY+BLKM1M2UNITSSheet Resistance6.77.88.059.7313.60.080.08ohms/sqContact Resistance10.611.010.04.79ohmsGate Oxide Thickness 4190LY\_HRIM4M5M6N\_WUNITSPROCESS PARAMETERSM3POLY\_HRIM4M5M6N\_WUNITSSheet Resistance0.080.080.080.03930ohms/sqContact Resistance9.2414.0518.3920.69ohms

COMMENTS: BLK is silicide block.

| CAPACITANCE PARAMETERS | 5 N+ | P+ | POLY   | M1 | М2 | ΜЗ | M4 | M5 | М6 | R_W | D_N_W_M5P_N_W_U | NITS  |

|------------------------|------|----|--------|----|----|----|----|----|----|-----|-----------------|-------|

| Area (substrate)       | 942  | 11 | 63 106 | 34 | 14 | 9  | 6  | 5  | 3  |     | 123 125 aF,     | ′um^2 |

| Area (N+active)        |      |    | 8484   | 55 | 20 | 13 | 11 | 9  | 8  |     | aF,             | /um^2 |

| Area (P+active)        |      |    | 8232   |    |    |    |    |    |    |     | aF,             | /um^2 |

| Area (poly)            |      |    |        | 66 | 17 | 10 | 7  | 5  | 4  |     | aF,             | /um^2 |

| Area (metal1)          |      |    |        |    | 37 | 14 | 9  | 6  | 5  |     | aF,             | /um^2 |

| Area (metal2)          |      |    |        |    |    | 35 | 14 | 9  | 6  |     | aF,             | /um^2 |

| Area (metal3)          |      |    |        |    |    |    | 37 | 14 | 9  |     | aF,             | /um^2 |

| Area (metal4)          |      |    |        |    |    |    |    | 36 | 14 |     | aF,             | /um^2 |

| Area (metal5)          |      |    |        |    |    |    |    |    | 34 |     | 984 aF,         | /um^2 |

| Area (r well)          | 92(  | )  |        |    |    |    |    |    |    |     | aF,             | /um^2 |

| Area (d well)          |      |    |        |    |    |    |    |    |    | 582 | aF,             | /um^2 |

| Area (no well)         | 13   | 7  |        |    |    |    |    |    |    |     | aF,             | /um^2 |

| Fringe (substrate)     | 212  | 2  | 235    | 41 | 35 | 29 | 21 | 14 |    |     | al              | ₹/um  |

| Fringe (poly)          |      |    |        | 70 | 39 | 29 | 23 | 20 | 17 |     | al              | ₹/um  |

| Fringe (metall)        |      |    |        |    | 52 | 34 |    | 22 | 19 |     | al              | ∃/um  |

| Fringe (metal2)        |      |    |        |    |    | 48 | 35 | 27 | 22 |     | al              | ∃/um  |

| Fringe (metal3)        |      |    |        |    |    |    | 53 | 34 | 27 |     | al              | ∃/um  |

| Fringe (metal4)        |      |    |        |    |    |    |    | 58 | 35 |     | al              | ₹/um  |

| Fringe (metal5)        |      |    |        |    |    |    |    |    | 55 |     | al              | ∃/um  |

| Overlap (N+active)     |      |    | 89     | 5  |    |    |    |    |    |     | al              | ∃/um  |

| Overlap (P+active)     |      |    | 73     | 7  |    |    |    |    |    |     | al              | F/um  |

|                        |      |    |        |    |    |    |    |    |    |     |                 |       |

| CIRCUIT PARAMETERS      |     | UNITS  |             |  |  |  |  |

|-------------------------|-----|--------|-------------|--|--|--|--|

| Inverters               | K   |        |             |  |  |  |  |

| Vinv                    | 1.0 | 0.74   | volts       |  |  |  |  |

| Vinv                    | 1.5 | 0.78   | volts       |  |  |  |  |

| Vol (100 uA)            | 2.0 | 0.08   | volts       |  |  |  |  |

| Voh (100 uA)            | 2.0 | 1.63   | volts       |  |  |  |  |

| Vinv                    | 2.0 | 0.82   | volts       |  |  |  |  |

| Gain                    | 2.0 | -23.72 |             |  |  |  |  |

| Ring Oscillator Freq.   |     |        |             |  |  |  |  |

| D1024 THK (31-stg,3.3V) |     | 300.36 | MHz         |  |  |  |  |

| DIV1024 (31-stg,1.8V)   |     | 363.77 | MHz         |  |  |  |  |

| Ring Oscillator Power   |     |        |             |  |  |  |  |

| D1024 THK (31-stg,3.3V) |     | 0.07   | uW/MHz/gate |  |  |  |  |

| DIV1024 (31-stg,1.8V)   |     | 0.02   | uW/MHz/gate |  |  |  |  |

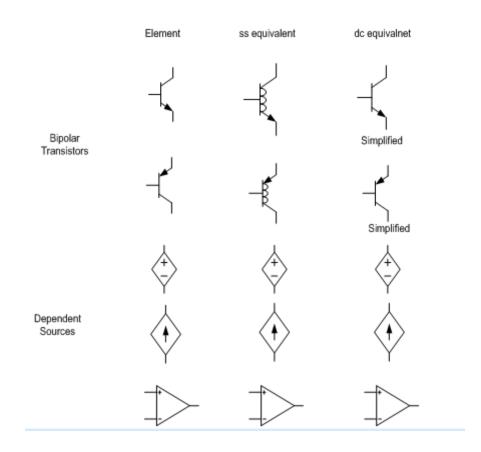

### Dc and small-signal equivalent elements